AMD EPYC Turin with as much as 192 Zen5 cores pictured

{Hardware} leaker YuuKi_AnS stocks the first actual footage of the next-gen AMD data-center processors.

AMD is gearing up for the release of a brand new sequence of EPYC processors, introducing the Turin Vintage and Turing Dense fashions with a Zen5 microarchitecture. Those processors boast as much as 128 Zen5 cores or a 192 Zen5c design. Significantly, the approaching CPU sequence will enhance DDR5-6000 reminiscence, along side CXL 2.0 and PCIe Gen5 requirements. They’re going to, then again, deal with socket compatibility with the prevailing SP5 socket.

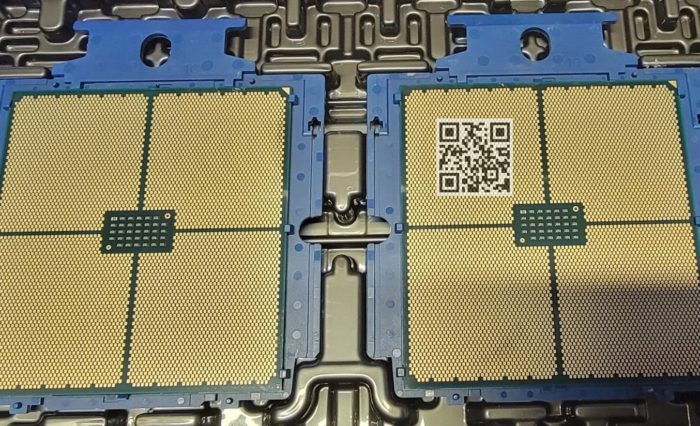

The brand new leak showcases new CPUs from more than a few angles, revealing that there’s no trade in design from the former Genoa (Zen4) sequence. On the other hand, a noticeable trade lies within the colour of the bracket used for transportation and socket set up, now carrying a definite blue hue. Whilst the leaked knowledge doesn’t explicitly determine the precise section displayed as an engineering pattern, the OPN code 100-00001245-07 and its 2023 manufacturing date are noteworthy.

AMD EPYC Turin 128/192 core CPUs, Supply: YuuKi_AnS

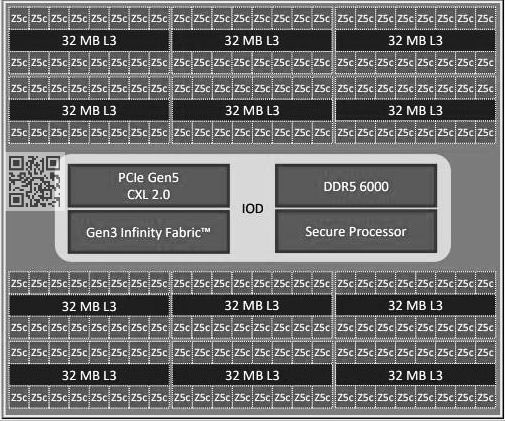

Accompanying those leaked photographs, YuuKi has shared two diagrams that verify the structure of the approaching CPUs. The vintage EPYC design is about to characteristic one IOD die and 16 CCDs, whilst the dense variant opts for 12 CCDs. Every compute chiplet will area its 32MB L3 cache, leading to a cumulative most L3 cache of 512MB.

AMD EPYC Turin 128/192 core CPUs, Supply: YuuKi_AnS

In accordance to different leaks, AMD may well be transferring clear of the ‘vintage’ and ‘dense’ core designators with the creation of the Zen6 structure. As an alternative, the corporate would possibly put it up for sale every EPYC sequence for a distinct crew of shoppers: common function, cloud, technical, and telecoms.

The disaggregated technique to chiplet design leaves AMD with many choices for more than a few configurations, the ones tiers is probably not the one segments that AMD is taking a look to fill. Moreover, AMD MI300 XPUs will sooner or later exchange some vintage CPU designs through integrating CPUs into one package deal. It’s imaginable that the way forward for EPYC sequence will glance other from what the corporate has established during the last few years.

| AMD EPYC Sequence | ||||||

|---|---|---|---|---|---|---|

| Sequence | Codename | Socket | Cores | L3 Cache | Reminiscence | Max TDP |

| Zen6 (2025+), PCIe Gen6 | ||||||

| EPYC 10006 (?) | Venice-Vintage | SP7 | TBC | DDR5-6400 (16ch) | TBC | |

| EPYC 10006 (?) | Venice-Access | SP8 | TBC | DDR5-6400 (4/8ch) | TBC | |

| Zen5 (2024), PCIe Gen5 | ||||||

| EPYC 10005 (?) | Turin Dense | SP5 LGA-6096 | DDR5-6000 (12ch) | |||

| EPYC 10005 (?) | Turin Vintage | SP5 LGA-6096 | DDR5-6000 (12ch) | |||

| Zen4 (2023), PCIe Gen5 | ||||||

| EPYC 9004 | Bergamo | SP5 LGA-6096 | DDR5-5600 (12ch) | |||

| EPYC 9004 | Genoa-X | SP5 LGA-6096 | DDR5-4800 (12ch) | |||

| EPYC 9004 | Genoa | SP5 LGA-6096 | DDR5-4800 (12ch) | |||

| EPYC 8004 | Sienna | SP6 LGA-4844 | DDR5-5200 (6ch) | |||

| Zen3 (2021), PCIe Gen4 | ||||||

| EPYC 7004 | Milan-X | SP3 LGA-4094 | DDR4-3200 (8ch) | |||

| EPYC 7003 | Milan | SP3 LGA-4094 | DDR4-3200 (8ch) | |||

Supply: YuuKi_AnS

Allow 48h for review and removal.